DFI X48 LT T2R: Floats like a Butterfly…

by Rajinder Gill on April 28, 2008 4:00 AM EST- Posted in

- Motherboards

Important Performance Related BIOS Options

DFI supplied us with their latest BIOS for testing, which is set to go live sometime this week in a public beta. There are six new options for MCH termination and reference voltage adjustments. Three of the new settings over-complicate the BIOS to the point of being unnecessary so will probably be dropped for the public beta. The remaining three BIOS functions will be documented in this guide with the little information we have - even DFI is unsure as to their true nature and Intel has not been forthcoming with the information, shrouding these settings in further mystery.

For the most part, please note that we have decided to work on explanations of BIOS settings we deem worthy of user adjustment when overclocking. Settings we have left out were found to function adequately at the default/AUTO settings.

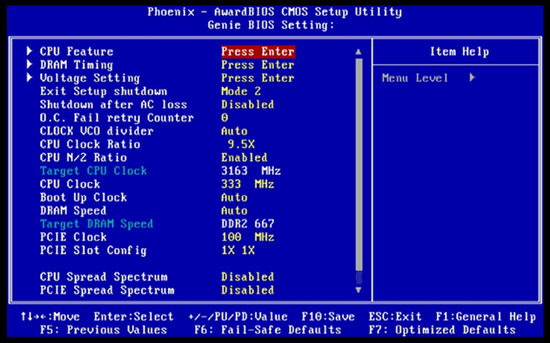

Genie BIOS Setting

|

Boot Up Clock: Sets a safe user selected FSB speed for the system to revert to when an overzealous overclock fails.

PCIE Clock: Overclocking the PCIE bus can be useful for benchmarking, bringing small gains to overall scores. Unfortunately the X48/ICH9R combo does not have the potential for overall MHz we find with NVIDIA's 680i chipset which could run PCIE frequencies in excess of 150MHz for benchmarking. Generally, speeds below 110 MHz are safe enough to use, while SATA detection begins to fail when frequency is increased above 115MHz.

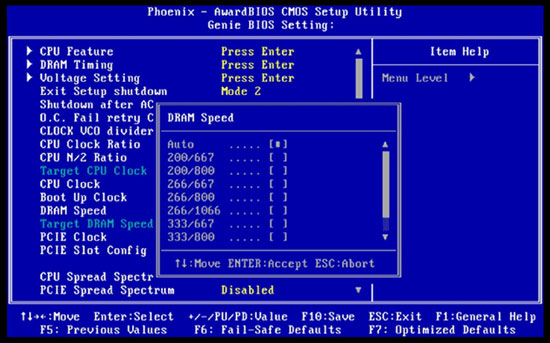

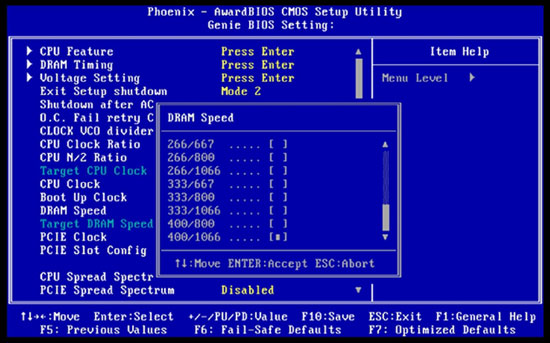

DRAM Speed

Available options are for this function can be seen in the following images:

|

|

We recommend that users with quad-core processors stay around 400FSB if they have the luxury of an unlocked multiplier. A 10x multiplier used at 400FSB will not require any GTL reference voltage adjustments to work and choosing the 266 strap will select a default tRD of 6 with some of the phases pulled down to 5 automatically in the BIOS. It really cannot get any simpler to set up one of these processors.

In fact, there are not any boards we know of that can quite eclipse this feat with 8GB of memory in place. We managed to run our board at default VMCH (1.25V) with a QX9650 and no less than 8GB of memory running DDR2-1000 and it was completely stable. Trying to beat this level of performance in any other way with 12MB cache quad-core CPUs is virtually impossible on this board. A default VTT voltage will get you close to 420 FSB, at which point a tRD adjustment as well as non-linear VTT increases for every 10FSB will follow.

We managed to get to 440FSB fully stable, but the VTT required was hardly safe for 24/7 use. As rule of thumb, do not exceed 1.34V (real), unless you have sub-zero cooling and are only running the board to perform a few benchmarks.

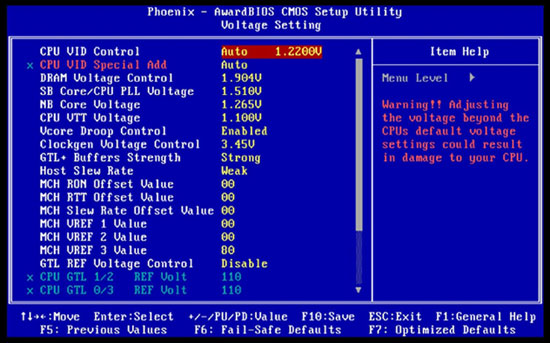

|

CPU VID Control: This function sets the current CPU Vcore (range from 0.8V to 1.6V); this function can be used in conjunction with "CPU VID Special Add", for overvolting past 1.6V if required.

CPU VID Special Add: Used in conjunction with "CPU VID Control", sets a percentage of VCore over the applied voltage using the "CPU VID Control" function; maximum is 125% over 1.6V.

VCore Droop Control: We generally leave this function to its default setting of Enabled. Using Enabled here ensures that the applied VCore is never compromised by overshoot while the PWM circuit is recovering for a heavy transient load. Disabling this function will remove the droop but will also strain the MOSFETs as they struggle to maintain the applied Vcore level, which fluctuates thousands of times a second from the applied value even in light load conditions. The recovery process with no Voffset usually results in longer settling times, which actually gives rise to instability in certain cases - a BSOD during the windows load process is a classic example of this at work.

NBCore Voltage: Sets the core voltage for the MCH. For quad-core CPUs, operating under 420FSB may require nothing more than 1.32V. Over 430FSB, the VMCH requirement rises quite drastically, making the whole process futile - especially when we consider that a rather loose tRD value is required just to hold the board stable. For dual-core processors, if properly tuned the VMCH requirement can be as low as 1.4V for benchmarking while full stability will need circa 1.55V. A properly tuned NBGTL reference voltage value, VTT, and MCH reference values all serve to reduce the requirement of higher levels of VMCH. Anything over 510FSB using a 45nm processor will require in excess of 1.6V though.

CPU VTT Voltage: VTT is the termination voltage used to string data lines between the CPU FSB and the MCH. Increasing this voltage usually enables FSB frequency to be increased. Both 65nm and 45nm processors can benefit from a slight overvolt, bearing in mind that GTL voltage values must be tuned effectively any time an adjustment is made to VTT. For 65nm dual- and quad-core processors we recommend that users attempt to overclock their systems without any adjustment to VTT and GTL and see how far the board will clock.

We have heard of instances where pushing 65nm quad-core processors to their internal FSB limits before any adjustment of VTT/GTL is necessary when using this board. For 45nm quad-cores, we have already outlined our thoughts on the sensible operating point at the beginning of this guide, which just so happens to not require any adjustment to VTT or GTL values.

Pushing dual-core 45nm processors requires no real adjustment to VTT or GTL right up to 485FSB on our board. After this point, we find that although we can run VTT levels in the region of 1.18-1.28V to benchmark the board, heavy CPU loads result in a system freeze irrespective of GTL tuning until we raise VTT to around 1.34V (real) and set GTL reference values in the region of 61% of VTT. The bottom line here is that many users should never need to alter VTT/GTL levels unless they happen to have Satan's donkey for a processor or are shooting for high FSB levels for their particular processor class.

MCH Vref 1/2/3 Value

The defaults for these three settings are 00/00/80. DFI informed us that all three settings must be moved in unison, i.e. the ratio between all three settings should be maintained if making any adjustments. Up to 500 FSB, adjustment of these three settings is not usually necessary (though the FSB threshold for required adjustment may be lower for quad-cores). Unfortunately, there is little information available to us as to exactly which part of the MCH is driven by these reference voltages.

However, through some fiddling, we have found that a value of 30/30/B0 works quite well on our board once beyond 500FSB with a 45nm dual-core CPU. Effects can be marginal at times and at others provide the MCH with enough offset to boot into the OS and allow a benchmark to run. With a hexadecimal scale ranging from 00 to FF, the permutations for adjustment are almost limitless.

We found values over 40/40/C0 did not provide us with any additional gain. Properly set, the ability of the board to run low levels of VMCH may become apparent for those who run just benchmarks. We managed to 3D benchmark our board right down at 1.4VMCH at 500FSB and 4GHz with an E8500 CPU with 4GB of memory when this setting was tuned for our board and parts combination, something we have not be able to do on any other X48 board in DDR2 form.

24 Comments

View All Comments

lopri - Monday, April 28, 2008 - link

Sorry if I missed it but I can't locate it?Rajinder Gill - Monday, April 28, 2008 - link

Hi,There is no PDF, it is an Adobe flash player video on page 14..

regards

Raja

Kromis - Monday, April 28, 2008 - link

I'm loving the green!Kromis - Monday, April 28, 2008 - link

I haven't heard/read much from DFI in a while